Technology Labs

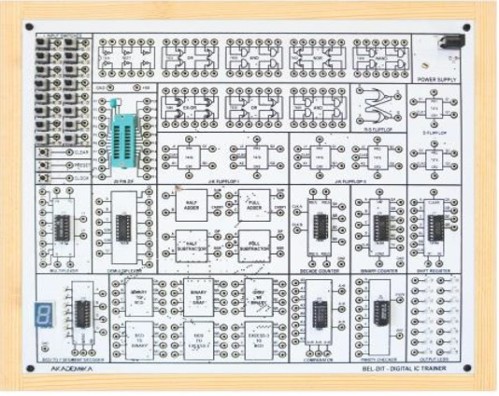

BEL-DIT: Digital IC Trainer

About Product

CPLD-based system that replicates logic ICs, counters, registers, arithmetic circuits, code converters & decoders. Optional manual clock, LED outputs, MUX/DEMUX, parity generator and 7-segment interface provide real-hardware digital design experience aligned with fundamental digital electronics curriculum.

Single board system capable of covering minimum 10 experiment.

Designed using a Lattice CPLD Chip LC4128ZE covering all the Digital IC's as mentioned in the specification.

IEEE Symbol of all components provided on the PCB.

Basic logic gate IC

NOT (IC-7404), OR (IC-7432), AND (IC-7408), NOR (IC-7402), NAND (IC-7400), EX-0R (IC-7486), EX-NOR(74266)

NAND and NOR gates as universal logic gates

De-Morgan's theorem I and II

Boolean equation

Half adder, full adder, half subtractor, full subtractor

Flip-Flops RS (using NOR), JK(7476), D (IC-7474), MS-JK , D (IC-7474) and T (using JK

Ripple counter (IC-7490)

Synchronous binary counter (IC-74191)

4-bits ring counter using (IC-7476)

Decade / BCD counter using IC-7490

Universal shift register IC-74194

9-bits parity generator / checker (IC-74280)

Multiplexer (IC-74153) and De-multiplexer (IC-74138)

BCD to seven segment decoder (IC-7447) and seven segment display

4-bits comparator (IC-7485)

Code Converter: Binary to Gray, Gray to Binary, Binary to BCD, BCD to Binary, BCD to Excess-3, Excess- 3 to BCD

16 Switches to provide logic 0 and 1 inputs with indication

16 LEDs to observe the output logic states

Manual clock, preset and clear to observe the counter operation

To verify the truth table and function of basic logic gates

To verify NAND and NOR gates as universal logic gates

To verify the De-Morgan's theorem I and II

To verify the Boolean equation

To study and verify working and truth table of half adder, full adder, half subtractor and full subtractor

Design of half adder and half subtractor using multiplexer and de-multiplexer

Study the behavior of basic flip-flops (RS, JK, MSJK, D , T)

To study and design ripple/ asynchronous counter using JK flip-flop

To study the synchronous binary counter using IC-74191

To design 4-bits ring counter using JK øip-øop

To verify decade / BCD counter using IC-7490

To study universal shift register using IC-74194

To study 9-bits parity generator / checker using IC-74280

To study multiplexer IC-74153 and de-multiplexer IC-74138

To study BCD to seven segment decoder IC-7447

To study 4- bits comparator IC-7485

• To study Binary to Gray, Gray to Binary, Binary to BCD, BCD to Binary, BCD to Excess-3, and Excess-3 to BCD converters

To study 4-bits binary adder

Study of TTL clock generation using NAND gate

Study of de-bounce circuit using NAND gate

With 35 years of legacy in Technical Education, Akademika extends its expertise to Defence and Skill development, building Innovative, Reliable Training Systems for the next generation of Learners.